#Synplicity synplify pro down software

You do not need to set any initialization or project variables before using Synplicity software with For information on the other directories that are created during Quartus II installation see "Quartus II File Organization" in the Quartus II Installment & Licensing for PCs and the Quartus II Installation & Licensing for UNIX and Linux workstations manuals.Ĭontains the Altera-provided Library Mapping File, synplcty.lmf, which maps Synplicity logic functions to equivalent Quartus II logic functions. Make sure the appropriate Quartus II/Synplicity interface subdirectories have been created in the Quartus II system directory (by default, the /usr/quartus directory on UNIX workstations and the \quartus directory on PCs) during Quartus II installation. After installation, you can open the Release Notes and readme.txt file from the Quartus II Help menu. You should read the Release Notes and readme.txt file before installing the Quartus II software. The Quartus II readme.txt file provides information on installation and operating requirements. The Quartus II Software Release Notes are available on the Altera web site and provide up-to-date information on which versions of Synplify applications are supported by the current version of the Quartus II software. This version of the Synplify software supports all Altera devices supported by the Quartus II software. VHDL & Verilog Synthesis for FPGAs and CPLDs

Make sure you have installed the correct versions of the Quartus II software and the Synplify software: To set up the Synplify working environment:

#Synplicity synplify pro down install

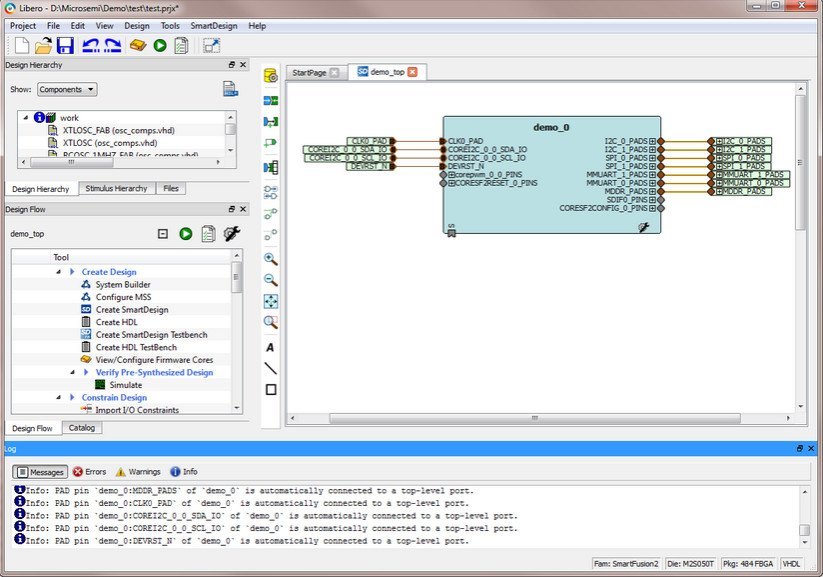

To use the Quartus ® II software with the Synplicity Synplify software, you must first install the Quartus II software, then establish an environment that facilitates entering and processing designs. Using the Synplify Software with the Quartus II SoftwareĬreate a Design for Use with the Synplify Software The Synplify 6.1 starts at $9,000 and Synplify Pro 6.1 starts at $19,000.Using the Quartus II Software with Other EDA Tools In addition, both Synplify Pro and Synplify include new quality of results improvements for Xilinx Virtex-I I FPGAs, including Dynamic shift-register-lookup (SRL) support, automatic inference of up/down counters and support for simultaneous read and write for BlockRAMs.īoth tools also include support for Altera's Apex20K and Apex20KE family of devices and support for Triscend's A7 and E5 hybrid standard cell/programmable devices Actel 54SXS and eX families Lattice SuperFast and SuperWide families Lucent Orca4 family and QuickLogic QuickDSP family. Garrison said that by using Synplify Pro in the Modular Design Flow, design team leaders can define modular boundaries for each team member and generate separate netlists and constraints for each section of the design.

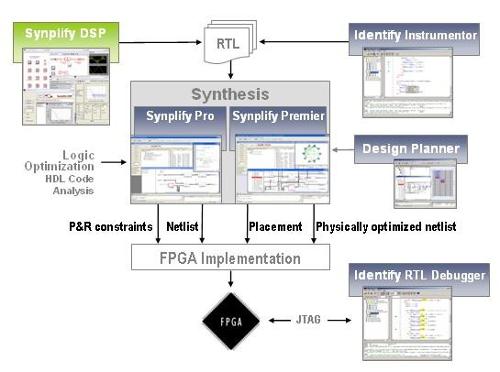

Version 6.1 of Synplify Pro also includes support for Synopsys' Stamp modeling format and support for the Xilinx Modular Design Flow. The Synplify Pro software enables communication between the cores, eliminating the need to reimplement the core and allowing individual design team members to work on a design with the language to which they are most accustomed. Traditionally, a designer would have to manually reimplement a core if it were written in a language different from the primary language of the design. Garrison said the new mixed-language sup port will allow designers to mix and match Verilog or VHDL into their designs. The tool also improves the quality of results for Xilinx Virtex-II devices and Altera Apex20K/E families, Garrison said, while adding new support for devices from Actel, Lattice Semiconductor, Lucent, QuickLogic and Triscend. The three new capabilities, he said, "will help greatly to knock down those barriers." "With this release, we are trying to break down some of the barriers for integrating IP into FPGA designs," said Jeff Garrison, director of FPGA products for Synplicity (Sunnyvale, Calif.). Key new features included in version 6.1 are mixed-Verilog and VHDL support, timing modeling in Synopsys Inc.'s Stamp format and support for Xilinx Inc.'s Modular Design Flow. has enhanced its Synplify Pro FPGA synthesis tool to better support designers integrating intellectual property (IP) cores into high-density FPGAs. Synplicity adds IP savvy to FPGA synthesis tool By Michael Santarini, EE Times Novem(4:13 p.m. Synplicity adds IP savvy to FPGA synthesis tool

0 kommentar(er)

0 kommentar(er)